| Uploader: | Gorg |

| Date Added: | 15 October 2013 |

| File Size: | 31.97 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 54009 |

| Price: | Free* [*Free Regsitration Required] |

This chip has two uses:. From the perspective of a software application, this is really just another way to call a subroutine, but with a twist. Some example code would be like this:. Instead it moves on immediately to the stop bits, and is an admission that parity checking at this level is really useless.

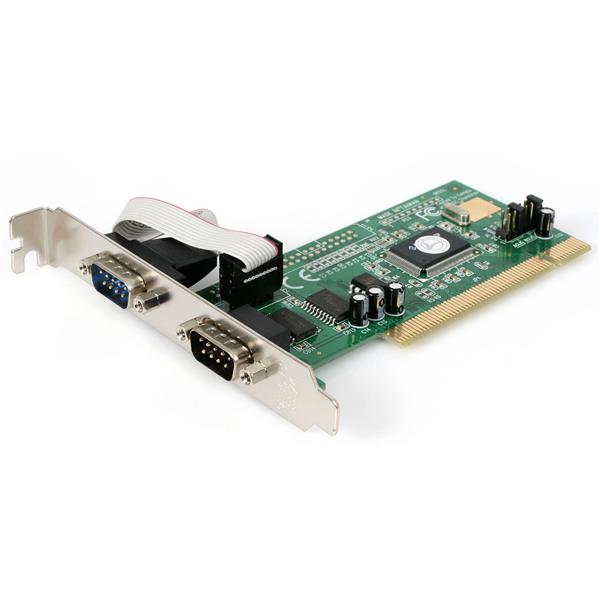

16550 UART

Interfaces are listed by their speed in the roughly ascending order, so the interface at the end of each section should be the fastest. If you are instead trying to write your own operating system, you would have to write these interrupt handlers directly, and establish the protocol on how you access these handlers to send and retrieve data. The following table explains some of the details of this register, and what each bit on it represents:. Other operating systems like Linux or MS-Windows use the approach of having a "driver" urat hooks into these interrupt handlers or service routines, and then the application software deals with the drivers rather than dealing directly with the equipment.

Serial Programming/8250 UART Programming

In other words, at thousand times per second a counter is going down to determine when to send the next bit. Parity errors Bit 2 can also indicate a mismatched baud rate like the framing errors particularly if both errors are occurring at the same time.

To overcome these shortcomings, the series UARTs incorporated a byte FIFO buffer with a programmable interrupt trigger of 1, 4, 8, or 14 bytes.

Does all this sound confusing? There is no way to predict when a certain device is going to "request" an interrupt, so often multiple devices can be competing for attention from the CPU. Remember as well that this is trying to build a foundation for serial programming on the uwrt side.

When it was built, there was only one chip on the motherboard.

This even gives you the ability to "turn on" or "turn off" the FIFO. Bit 2 controls how many stop bits are transmitted by the UART to the receiving device. This buffer can be as small as 1KB to as large as 1MB, and depends substantially on the kind of data that you are working with.

It may take some time to hunt down these settings, and it is important to know what pkrt values are when you are trying to write your software.

There is quite a bit of information packed into each of these registers, and the following is an explanation for the meaning of each register and the information it contains. This primary port address is what we will use to directly communicate with the chip in our software. Bits 6 and 7 describe the trigger threshold value.

This comes from other scientific areas like rocket science where delta-vee means a change in velocity. Because some software had already been written to work with the FIFO, this bit Bit 7 of this register was kept, but Bit 6 was added to confirm that the FIFO was in fact working correctly, in case some new jart wanted to ignore the hardware FIFO on the earlier versions of the chip.

Usually the software really doesn't care, but on some rare occasions you really need to know this fact.

Install Serial Devices with a UART-Compatible Interface - Windows drivers | Microsoft Docs

seriaal Yes, you read that correct, 12 registers in 8 locations. Essentially, this deals with the other wires in the RS standard other than strictly the transmit and receive wires.

Before you think I don't know how to count or do math, we need to do a little bit of a history lesson here, which we will finish when derial move on to the chip. This is a relatively "new" register that was not a part of the original UART implementation.

For the purposes of this register, each of these bits will be a logical "1" the next time you access this Modem Status register if the bit it is associated with like Pirt Data Carrier Detect with Carrier Detect has changed its logical state from the previous time you accessed this register. Do not set the value "0" for both Divisor Latch bytes.

Meanwhile, we provide the following representative results each in a new pop-up window:. The following tables show the related bits to change in order to enable or disable each of the hardware interrupt devices:. When it is "1", that means the interrupt has already been processed or this particular UART was not the triggering device.

External devices are directly connected to this chip, or in the case of the PC-AT compatibles most likely what you are most familiar with for a modern PC it will have two of these devices that are connected together. Retrieved from " https: Technical and de facto standards for wired computer buses.

No comments:

Post a Comment